# **Hammer VLSI Flow**

Palmer Dabbelt, Edward Wang, John Wright, Colin Schmidt, **Harrison Liew**, Daniel Grubb, and many others, Borivoje Nikolić, Krste Asanović, Jonathan Bachrach

Berkeley Architecture Research

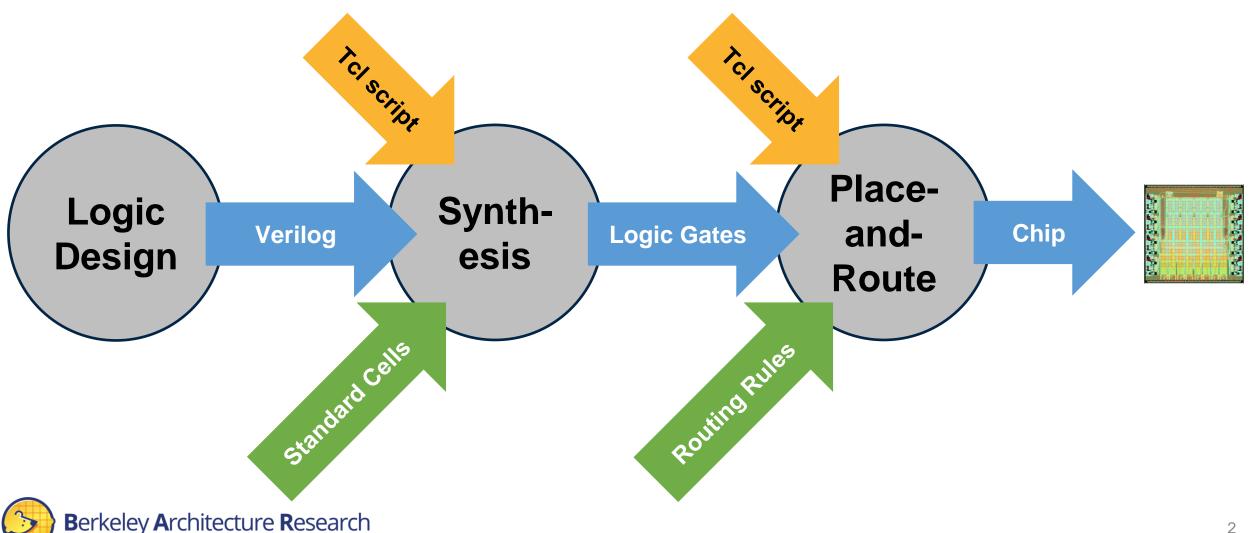

### Motivation: "Advertised" VLSI Flows

шш

ဗီ

### Motivation: "Advertised" VLSI Flows

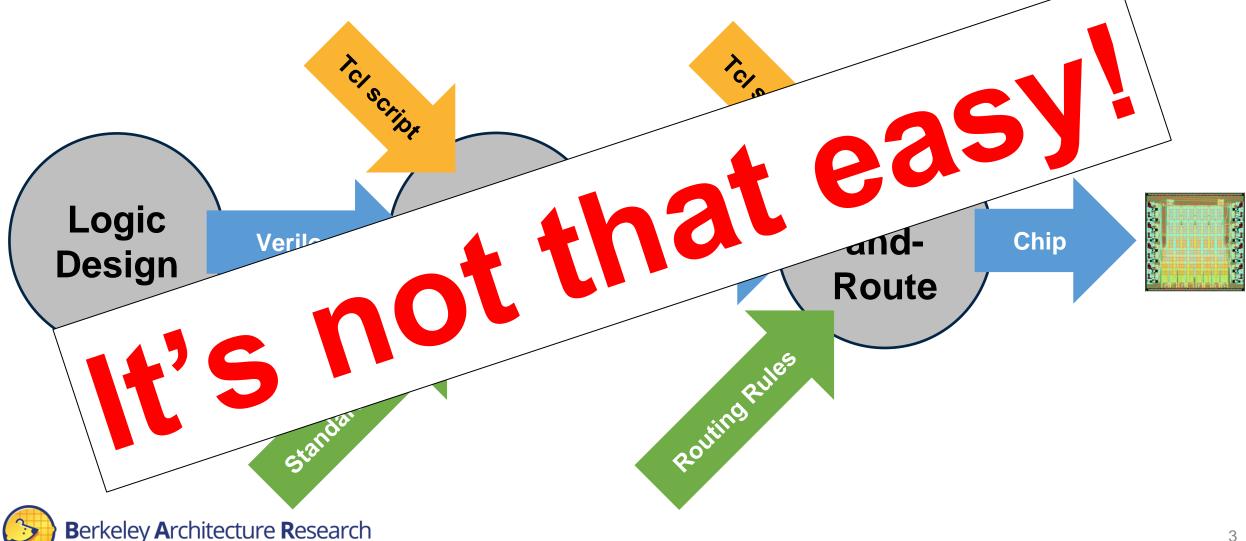

### Motivation: Real VLSI Flows

# Motivation: Real VLSI Flows

- Problem: VLSI flows must be rebuilt for each project

- Overhead compounded by

- Changing CAD tools

- Commands / features change

- File formats / library locations

- New process technology

- SRAMs (compiled/pre-generated?)

- DRC rules

- Different design

- Floorplanning / power / clock

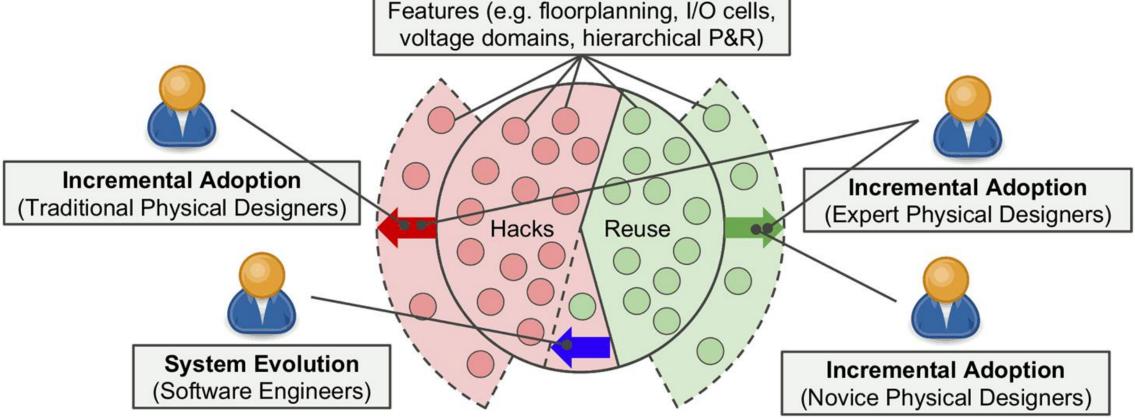

- · Goal: generate modular, reusable VLSI flows

- · Philosophy:

- Incremental Adoption

- Users: reuse what you can, hack what you can't

- System Evolution

- Devs: generalize hacks for future users

- Modularity + Abstraction = Clarity

- Separate concerns, standardize data exchange

## Hammer Design Philosophy

Using modularity and abstractions, HAMMER is designed to support incremental adoption and system evolution.

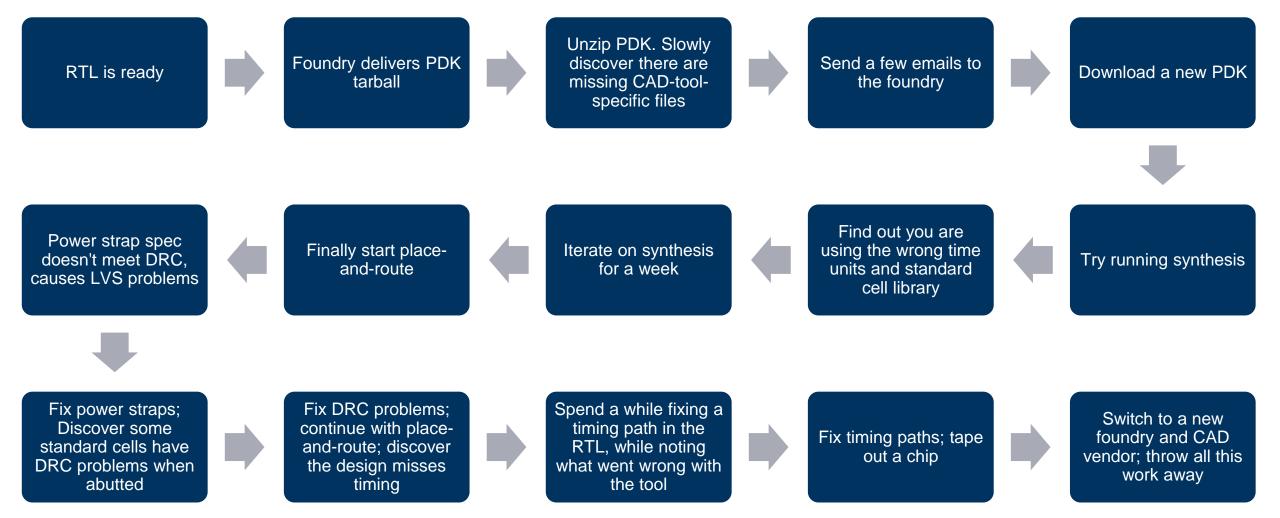

# Hammer Design Philosophy

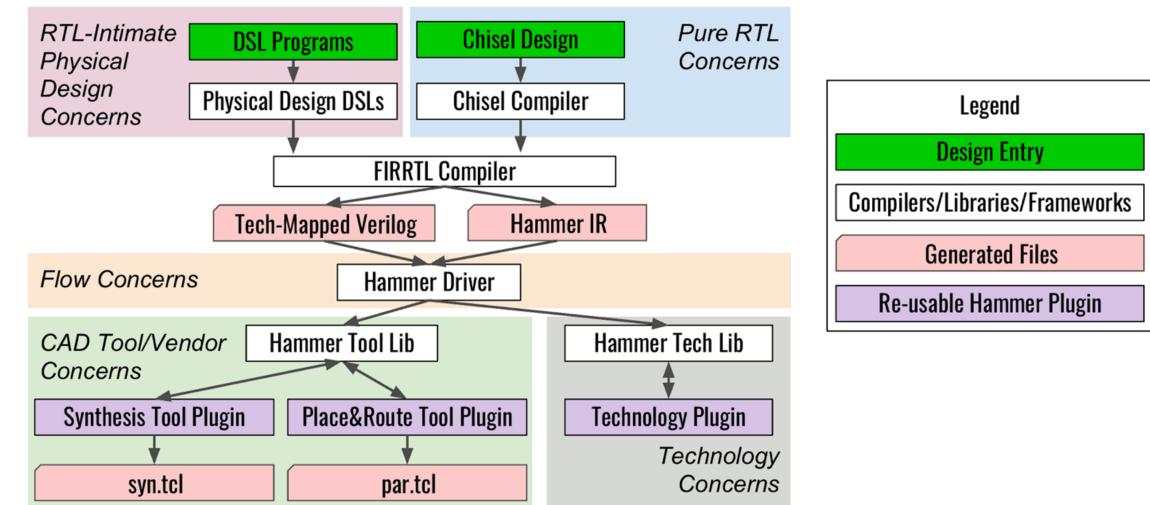

#### Separation of Concerns

- 3 input categories:

- 1. Design-specific

- 2. Tool/Vendor-specific

- 3. Technology-specific

#### Hammer IR

- Standard YAML/JSON input & data exchange format

- Metaprogramming: modifiable attributes

- Modular tech & tool plugins

- Default settings, flow steps, helper methods

- Interchangeable + extensible = reusable!

#### Design:

- Floorplan

- Clocks

- Hierarchy

#### Tool:

- In/out files

- Tcl code

- Tech. file formats

### Tech.:

- SRAMs

- Std. cells

- Stack-up

- Power straps

### Software Architecture

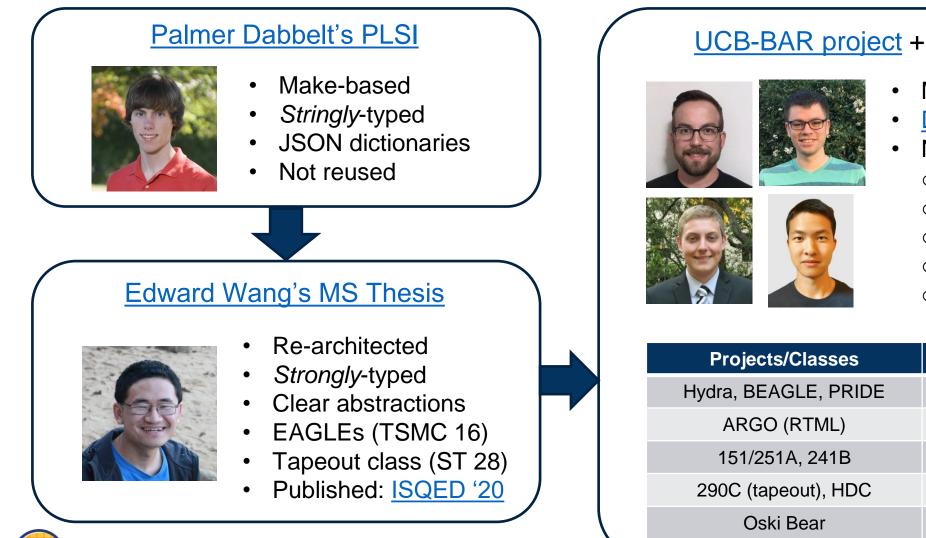

# History of Hammer

Berkeley Architecture Research

#### <u>UCB-BAR project</u> + <u>Chipyard integration</u>

- Many more devs

- Documentation

- New plugins & features

- $\circ$  RTL/gate-level simulation

- o DRC/LVS

- Power, EM/IR analysis

- o SRAM, PCB collateral

- APIs: power straps, bumps, pins, floorplan

| Projects/Classes     | Technology   |

|----------------------|--------------|

| Hydra, BEAGLE, PRIDE | Intel 22     |

| ARGO (RTML)          | GF 12        |

| 151/251A, 241B       | ASAP 7       |

| 290C (tapeout), HDC  | TSMC 28      |

| Oski Bear            | Skywater 130 |

# Current State + Future of Hammer

- Hammer is for everyone!

- Tape out in many process techs

- Arch. DSE with open-source techs

- Reusability regardless of design

- Current key features:

- Bottom-up hierarchical

- SRAM library compilation

- Many APIs: e.g., power straps

- Floorplan visualization

- User & tech hooks (i.e., hacks)

- What we're planning:

- Metrics parsing, constraints feedback

- OpenROAD plugins

- LEC, characterization plugins

- Aspect-oriented Chisel floorplanning

- Abutment/partition-based hierarchical

- True multi-clock/power domain gen.

- Cloud compute, CI, IR validity checks

Hammer users are also developers!  $\rightarrow$  driven by projects + tapeouts

- Github: <u>https://github.com/ucb-bar/hammer/</u>

- Documentation: <u>https://hammer-vlsi.readthedocs.io/</u>

- Chipyard-specific documentation: <u>https://chipyard.readthedocs.io/en/dev/VLSI/index.html</u>

- User mailing list: <a href="mailto:hammer-users@googlegroups.com">hammer-users@googlegroups.com</a>

- Plugin access requests: <u>hammer-plugins-access@lists.berkeley.edu</u>

- Cadence, Synopsys, and Mentor